Réalisations

Atos – Nœud de cohérence de cache CHI AMBA 5

Certains de nos collaborateurs ont eu l’opportunité de participer activement à un projet de grande envergure au sein de l’initiative européenne Montblanc2020 , notamment pour le développement de EPI (European Processor Initiative).

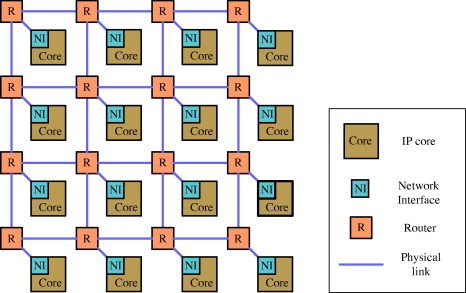

Notre contribution a porté sur la spécification et le développement de l’architecture d’une IP de cohérence de cache destinée à être utilisée avec des processeurs multicœurs ARM . Les nœuds de cohérence de cache interconnectés, conformes au protocole AMBA 5 CHI , jouent un rôle crucial en tant que coordinateurs entre la mémoire partagée et les différents cœurs du processeur. Cette orchestration hors du commun, destinée à un processeur comportant 128 cœurs logiques, gère un dernier niveau de cache, appelé « cache de niveau 3 » ou « last level cache » (LLC).

Notre implication dans ce projet a été fondamentale pour le développement de cette architecture de cohérence de cache sophistiquée, qui garantit une performance et une efficacité optimales pour des processeurs multicœurs. Ce projet démontre notre expertise avancée dans le domaine de la microélectronique, ainsi que notre engagement envers des initiatives de pointe en Europe.